大三上计组上课也没好好听课,老师给划的重点也和没划差不太多,只能硬着头皮来看书理解。这学期用的是还没出版的新教材,用的RISCV指令集。简单记录一下自己复习计组觉得重要的知识点。

第一章 计算机系统概述

表达式有 unsigned int 与 int 类型时,应按照无符号类型运算。

冯诺依曼基本思想

- 采用”存储程序”工作方式(计算机的工作由存储在其内部的程序控制)

- 计算器由运算器、控制器、存储器、输入设备和输出设备5个基本部件组成

- 存储器能存储数据和指令,形式上二者无区别,计算机应能进行区分

- 计算机内以二进制形式表示指令和数据,指令由操作码和地址码组成

CPU是由控制器、算数逻辑单元ALU、存储器等互连组成的电路。

CPU工作分为五个过程:取指、译码、执行指令、访存取数、结果写回。

计算机用户分类:最终用户、系统管理员、应用程序员、系统程序员。

计算机性能评价(主要考虑CPU性能)

- 基本指标:吞吐率和响应时间

- 时钟周期:CPU的主脉冲信号的宽度

- 时钟频率:CPU的主频,CPU时钟信号的倒数

- CPI:执行一条指令所需的时钟周期数

常用公式

- 用户CPU时间=程序总时钟周期数/时钟频率=程序总时钟周期数*时钟时间

- 程序总时钟周期数=程序总指令条数*平均CPI

- 用户CPU时间=CPI*程序总指令条数*时钟周期

- 时钟周期数=用户CPU时间*时钟频率

阿姆达尔定律

- 改进后的执行时间=改进部分执行时间/改进部分的改进倍数+未改进部分执行时间

- 整体改进倍数=1/(改进部分执行时间比例/改进部分的改进倍数+未改进部分执行时间比例)

第二章 数据的类型及机器级表示

从机器的角度看,数据只有整数、浮点数和位串这三类数据类型。

表示一个数值数据要确定三个要素:进位计数制、定/浮点表示和编码规则。

定点数:小数点位置约定在固定位置;浮点数:小数点位置约定为可浮动的数。

对于任意一个实数X,可以表示为X=(-1)s*M*RE

S为0或1,决定X的符号

M为二进制定点小数,称为数X的尾数

E是一个二进制定点整数,称为数X的阶或指数,常用移码表示,[E]移=偏置常数+E

R是基数,可以取值2、4、16等

数值数据在计算机内部编码表示后的数称为机器数。

n位有符号整数表示范围为-2n-1~(2n-1-1)。

n位无符号整数表示范围为0~(2n-1)。

32位浮点数表示方法

- 0位为数符位S

- 1-8位为8位移码表示的阶码E(偏置常数为128)

- 9-31位为24位二进制原码小数表示的尾数

- 小数点后面的1为隐藏位

32位IEEE754浮点数标准

格式

- 0位为数符位S

- 1-8位为8位移码表示的阶码E(偏置常数为127)

- 9-31位为24位二进制原码小数表示的尾数

- 小数点前面的1为隐藏位

分类

- 全0阶码全0尾数:+0/-0

- 全0阶码非0尾数:非规格化数

- 全1阶码全0尾数:+∞/-∞

- 全1阶码非0尾数:NAN

- 阶码非全0且非全:规格化非0数

字长等于CPU内部用于整数运算的运算器位数和通用寄存器宽度,表示数据运算、存储和传送的部件的宽度,反映了计算机处理信息的一种能力。

字用来表示处理信息的单位,用来度量各种数据类型的宽度。

大端方式为高位低地址,低位高地址,小端方式为低位低地址,高位高地址。

0扩展将高位补0,符号扩展将高位补符号位。

第三章 数据的运算及运算部件

高级语言运算类型

- 按位运算:&、|、~、^,按位运算的一个重要作用是实现掩码功能。

- 逻辑运算:&&、||、!,结果只有true和false两种结果

- 移位运算:<<、>>,分为逻辑移位和算数移位,注意是否会发生溢出

- 位拓展和位截断:0扩展用于无符号整数,符号扩展用于补码表示的带符号整数

基本运算部件

计算机中基本的运算部件是加法器、ALU和移位器,而ALU的核心部件是加法器。

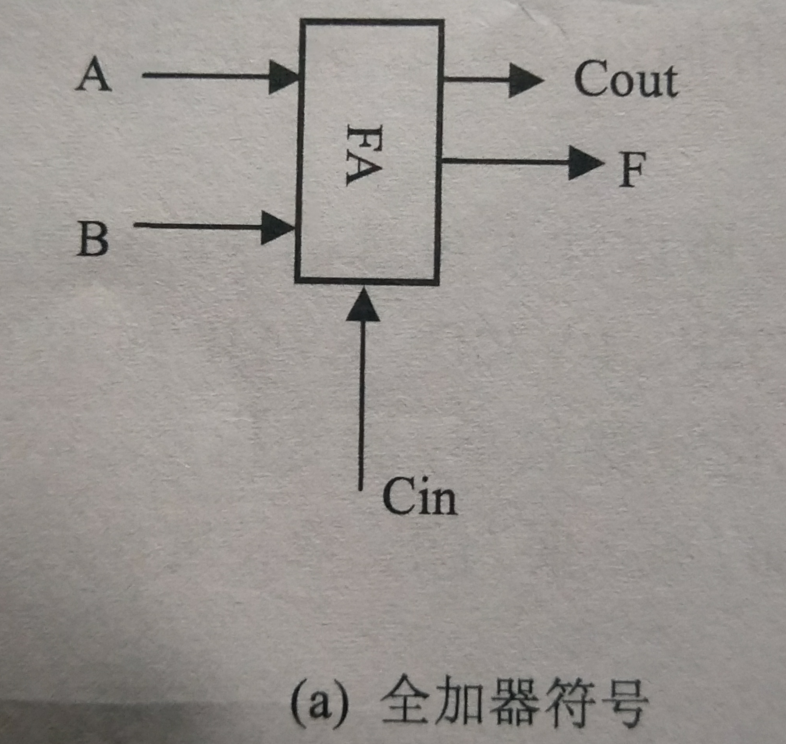

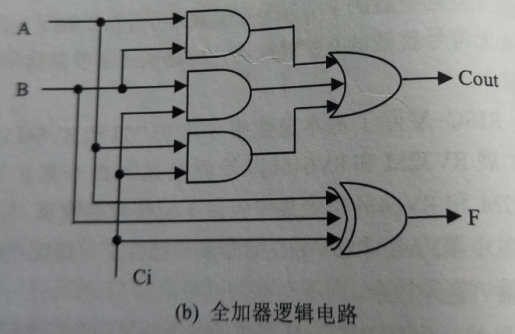

全加器

- 全加器的输入包括两个加数A和B,以及低位进位CIn,输出包括和F和高位进位Cout

- F=A^B^Cin

- Cout=A*B+A*Cin+B*Cin

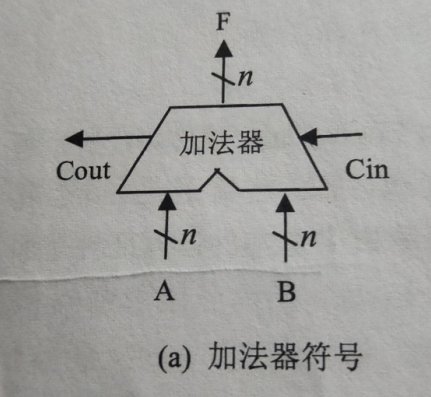

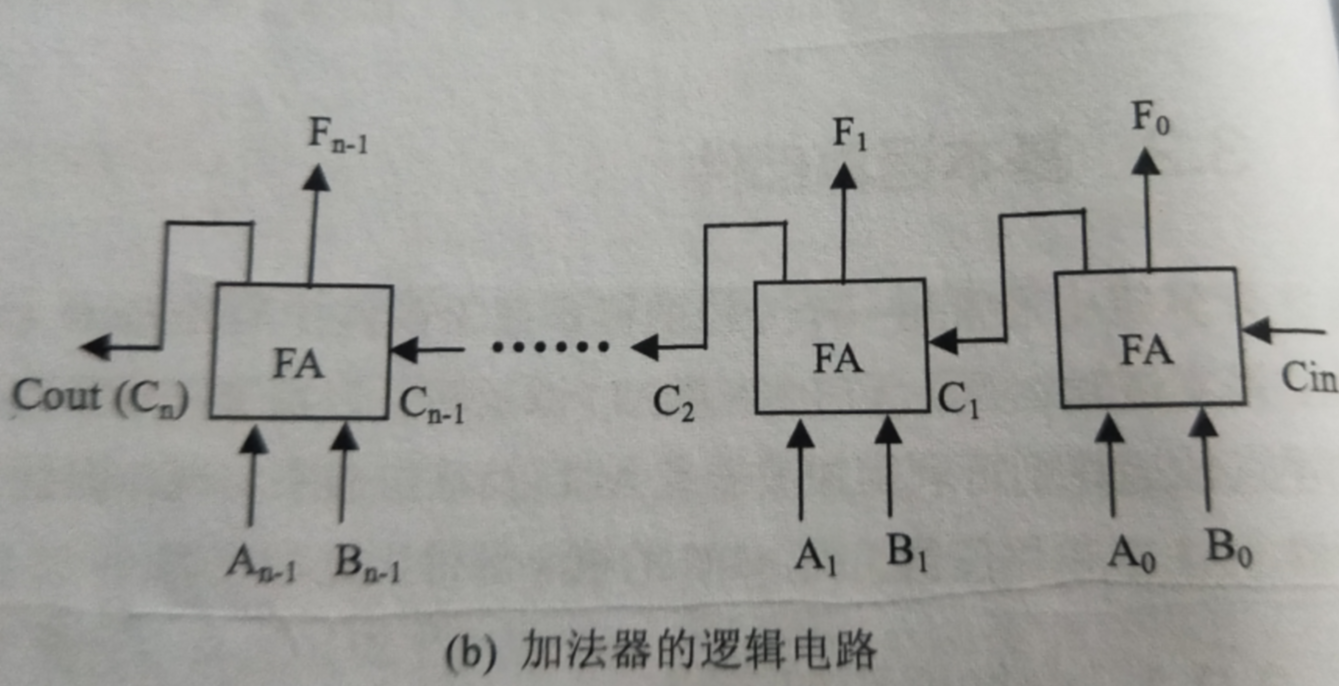

加法器

- n位加法器可由n个全加器实现。

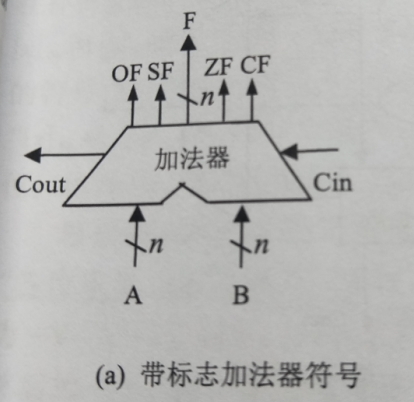

带标志加法器

- OF=Cn^n-1

- SF=Fn-1

- ZF=1当且仅当F=0

- CF=Cout^Cin

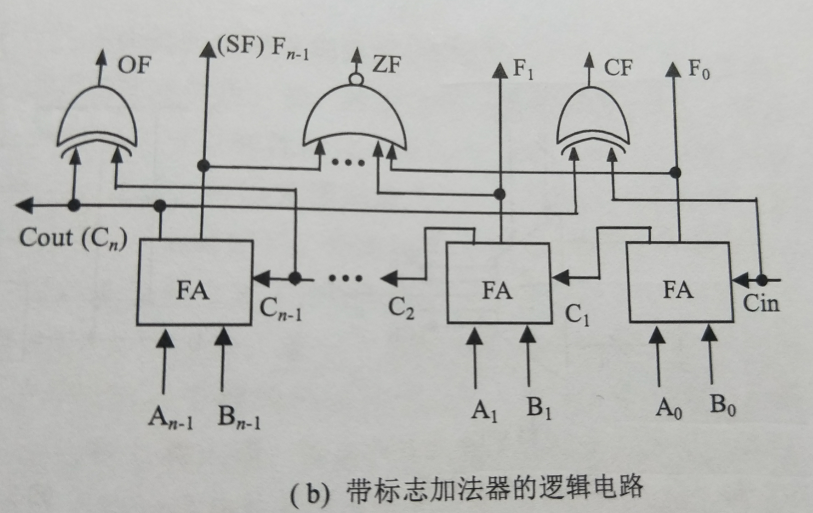

算术逻辑部件

算数逻辑部件ALU是一种能进行多种算数运算与逻辑运算的组合逻辑电路,其核心部件是带标志加法器,多采用先行进位方式实现。

- A和B是两个n位操作数输入端

- cin是进位输入端

- ALUop是操作控制端,决定CPU所执行的操作

定点运算机器运算部件

补码加减运算

[x+y]补=[x]补+[y]补(mod 2n)

[x-y]补=[x]补+[-y]补(mod 2n)

溢出判断

符号位产生的进位Cn与最高数值位向符号位的进位Cn-1不同

两个加数的符号位Xn-1与Yn-1相同,且与和的符号位Fn-1不同

原码加减运算

- 加法实行”同号求和,异号求差”,减法实行”同号求差,异号求和”

原码乘法运算

- 先确定乘积的符号位,再计算乘积的数值位

- 掌握原码一位乘法

补码乘法运算

原理与原码乘法相似

掌握布斯乘法

其他如补码除法运算等其他内容自行了解即可

浮点数运算部件

浮点数加减运算

- 对阶:小阶向大阶看齐,阶小的那个数的尾数右移,右移的尾数等于两个阶的差的绝对值

- 尾数加减:将IEEE754的隐藏位”1”,还原到尾数部分后进行加减运算

- 尾数规格化:对尾数进行右规或者左规

- 尾数的舍入处理:保证IEEE754格式,对小数点右边第23位后的数字进行舍入

浮点数乘除运算

浮点数乘法运算

第四章 指令系统及程序的机器级表示

指令格式设计

指令地址码的个数

- 一条指令中必须包含操作码、源操作数或其地址、结果的地址、下条指令地址。

- 根据指令给出的地址码个数分为三地址指令、二地址指令、单地址指令和零地址指令。

指令格式设计原则

- 指令应尽量短

- 要有足够的操作码位数

- 操作码的编码必须有唯一的解释

- 指令长度应是字节的整数倍

- 合理选择地址字段的个数

- 指令应尽量规整

指令系统设计

设计指令系统需要遵循完备性或完整性、兼容性、均匀性和可扩充性。指令系统设计的基本问题

- 操作码的个数、种类、复杂度如何选择?

- 运算指令能对哪几种数据类型进行操作?

- 采用什么样的指令格式?

- 通用寄存器的个数、功能、长度等如何规定?

- 如何设计寻址方式的种类和编码以及各种寻址方式下有效地址如何计算?

- 下条指令的地址如何确定?

操作数类型

- 指针或地址

- 带符号数数值数据

- 位、位串、字符和字符串

- 逻辑(布尔)数据

寻址方式

- 立即寻址

- 直接寻址

- 间接寻址

- 寄存器寻址

- 寄存器间接寻址

- 变址寻址

- 相对寻址

- 基址寻址

- 其他寻址

操作类型

- 算术和逻辑运算指令

- 移位指令

- 传送指令

- 串指令

- 顺序控制指令

- CPU控制指令

- 输入输出指令

操作码编码

- 定长操作码编码

- 扩展操作码编码

标志信息的生成和使用

- 零标志ZF

- 溢出标志OF

- 符号标志SF

- 进位/借位标志CF

指令系统设计风格

按操作数位置指令风格分类

- 累加器型指令系统

- 栈型指令系统

- 通用寄存器型指令系统

- Load/Store型指令系统

按指令格式的复杂度来分

- CISC风格指令系统

- RISC风格指令系统

RISC指令系统相对于CISC指令系统的主要特点有:

- 指令数目少

- 指令格式规整

- 采用Load/Store 型指令设计风格

- 采用流水线方式执行指令

- 采用大量通用寄存器

- 采用组合逻辑电路控制

- 采用优化的编译系统

异常和中断处理机制

- CPU内部产生的意外事件为内中断,称为”异常”

- CPU外部通过中断请求引脚INTR和NMI向CPU发出的中断请求为外中断,称为”中断”

异常

- 故障

- 自陷

- 终止

中断

- 由CPU外部的I/O部件发出,称为I/O中断

指令系统

- MIPS指令系统

- ARM指令系统

- IA-32指令系统

因为教材基于RISC-V架构,因为上面三种不详细展开

RISC-V架构中的机器级表示

RISC-V指令系统概述

- RISC-V介绍 点击查看

RISC-V 指令参考卡和指令格式

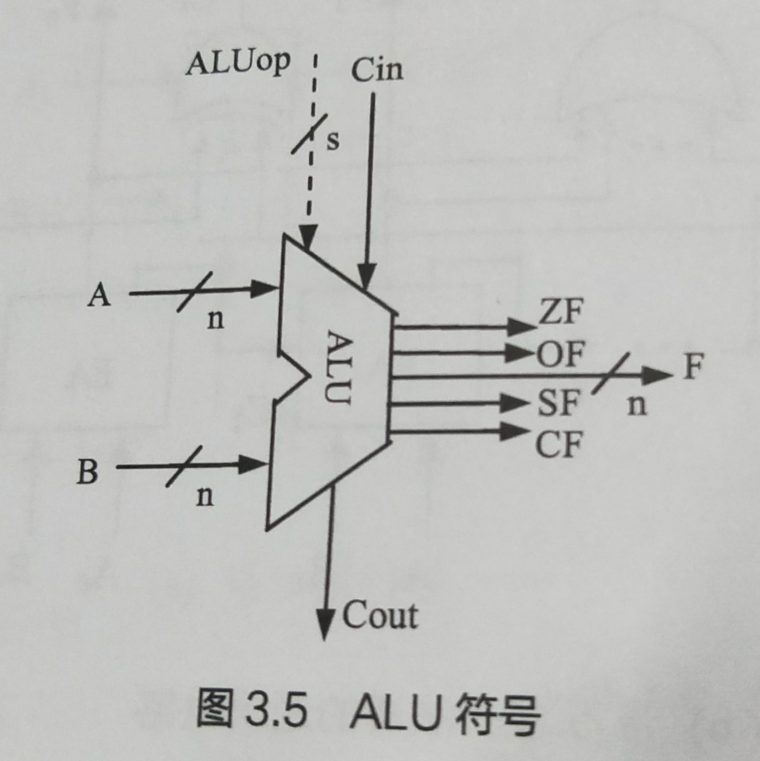

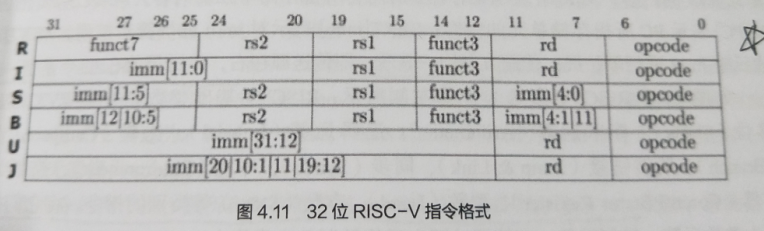

RISC-V采用32位定长指令字格式,如下图所示,共有6种指令格式

- R-型为寄存器操作数指令

- I-型为短立即数操作或装入(Load)指令

- S-型为存储(Store)指令

- U-型为长立即数操作指令

- B-型为控制转移类指令

- J-型为无条件跳转指令

所有指令格式的低7位都是操作码字段opcode;字段rd、rs1和rs2给出的是通用寄存器编号,32位RISC-V架构共有32个32位通用寄存器x0-x31,因而通用寄存器编号占5位,imm字段给出的是一个立即数,位数在[]中给出,字段funct3和funct7分别表示3位功能码和7位功能码,它们和opcode字段一起定义指令的操作功能。

RISC-V 基础整数指令集

- 整数运算类指令

- 控制转移类指令

- 存储器访问类指令

- 系统控制类指令

RISC-V过程调用约定

- 过程调用的执行步骤

- RISC-V中用于过程调用的指令

- RISC-V寄存器使用约定

- RISC-V中的栈和栈帧

- RISC-V的过程调用

RISC-V程序的转换、链接与加载

- 可执行文件生成概述

- RISC-V汇编器

- RISC-V链接器

第五章 中央处理器设计

CPU指令概述

指令执行过程

CPU执行一条指令的大致过程如下:

- 取指令

- 对IR中的指令操作数译码并计算下条指令地址

- 计算源操作数地址并取源操作数

- 数据操作

- 目的操作数地址计算并存结果

CPU的基本功能和基本组成

CPU由数据通路和控制部件两大基本部分组成

数据通路包括ALU、通用寄存器、状态寄存器、cache、MMU、福点运算逻辑、异常和中断处理逻辑等。

控制逻辑包括程序计数器(PC)、指令寄存器(IR)、指令译码器、时钟信号和控制信号的生成部件、总线控制逻辑、中断机构等。

数据通路的基本结构

指令执行需要用到组合逻辑元件(操作元件)和存储元件(状态元件)。

数据通路就是由操作元件和存储元件通过总线和分散方式连接而成的进行数据存储、处理和传送的路径。

组合逻辑元件

组合逻辑元件的输出只取决于当前的输入,如多路选择器(MUX)、加法器(Adder)、算术逻辑部件(ALU)、译码器(Decoder)等。

状态元件

状态元件具有存储功能,输入状态在时钟控制下被写到电路中,并保持电路的输出值不变,直到下一个时钟到达。

暂存寄存器和通用寄存器组。

数据通路和时序控制

- 早期计算机的三级时序系统

- 现代计算机的时钟信号

单总线数据通路

- 在通用寄存器之间传送数据

- 完成算术、逻辑运算

- 从内存读取一个字(指令或数据或数据的地址)

单周期CPU设计

处理器设计过程如下

- 分析每条指令的功能

- 根据指令的功能给出所需的元件,并考虑如何将它们相连

- 确定每个元件所需控制信号的取值

- 汇总所有指令涉及的控制信号,生成反映指令与控制之间的关系表

- 根据关系表,得到每个控制信号的逻辑表达式,据此设计控制电路

以9条RV32I指令作为实现目标

1 |

|

emmm,回家没带计组书,回去补上后面内容。

本文链接: https://yd0ng.github.io/2020/01/02/%E8%AE%A1%E7%BB%84%E5%A4%8D%E4%B9%A0/

版权声明: 本作品采用 知识共享署名-非商业性使用-相同方式共享 4.0 国际许可协议 进行许可。转载请注明出处!